Practicas De Electrónica Digital

This document was uploaded by user and they confirmed that they have the permission to share it. If you are author or own the copyright of this book, please report to us by using this DMCA report form. Report DMCA

Overview

Download & View Practicas De Electrónica Digital as PDF for free.

More details

- Words: 13,113

- Pages: 52

Loading documents preview...

Universidad Nacional Autónoma de México Facultad de Estudios Superiores Cuautitlán Departamento: Ingeniería Sección: Electrónica

Manual del Laboratorio de Sistemas Digitales Clave Carrera: 130 Clave de Asignatura : 1525

Autores : M. en TI. Jorge Buendía Gómez Ing. Jose Luis Barbosa Pacheco

Fecha de Elaboración: 2015 Fecha de modificación: Julio 2017

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Índice Índice

I

Prólogo

II

Reglamento

VI

Práctica 1

Herramientas de prueba para sistemas digitales 1.1. Sistemas digitales y analógicos.

1

Práctica 2

Compuertas lógicas integradas 2.2. Compuertas lógicas básicas, sus tablas de verdad y sus expresiones de Boole.

4

Práctica 3

Compuertas lógicas derivadas 2.2. Compuertas lógicas básicas, sus tablas de verdad y sus expresiones de Boole.

9

Práctica 4

Circuitos combinacionales por álgebra de Boole 2.4. Descripción algebraica de circuitos lógicos.

13

Práctica 5

Circuitos combinacionales con mapas de Karnaugh 3.6. Método de simplificación a través del mapa de Karnaugh.

16

Práctica 6

Características de las familias lógicas 4.2. La familia Lógica Transistor – Transistor (TTL). 4.4. La familia Lógica Metal – Oxido – Semiconductor (MOS).

19

Práctica 7

Multiplexores y demultiplexores 5.3. Multiplexores y Demultiplexores.

24

Práctica 8

Unidad aritmético lógica (ALU) 5.4. Circuitos digitales para operaciones aritméticas binarias. 5.7. Unidades Aritmético Lógicas (ALU’s).

28

Práctica 9

Contador síncrono para control de motor de pasos 6.7. Aplicaciones de circuitos secuenciales.

32

Práctica 10

Autómatas finitos con máquinas de Moore y Mealy 6.8. Autómatas finitos. 6.8.1. Máquina de Mealy. 6.8.2. Máquina de Moore.

36

Práctica 11

Memorias ROM 7.5. Características de las memorias ROM.

41

Laboratorio de Sistemas Digitales

I

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Prólogo Objetivos generales de la asignatura

Al finalizar el curso el alumno será capaz de comprender y analizar sistemas electrónicos digitales combinacionales y secuenciales, así mismo será capaz de diseñar e implementar circuitos electrónicos digitales para resolver problemas prácticos.

Objetivos del curso experimental

El alumno aprenderá a manejar las herramientas y equipos utilizados en el laboratorio de Sistemas Digitales. El alumno analizará y comprenderá el funcionamiento de los circuitos electrónicos digitales y sus aplicaciones a circuitos con diseños prácticos. El alumno adquirirá las habilidades y las competencias necesarias para el análisis, diseño e implementación de circuitos electrónicos digitales.

Introducción Un sistema digital es aquel dispositivo electrónico destinado a la manipulación, transmisión, procesamiento o almacenamiento de señales digitales, las cuales sólo puedan tomar 2 valores discretos, cero o uno, denominados digitos binarios (Binary Digit) o bit. Los sistemas digitales son un arreglo de dispositivos electrónicos analógicos tales como resistencias, diodos y transistores, diseñados para procesar información representada en forma digital a través de 2 voltajes de corriente directa, usualmente 0V y 5V.

Figura P.1 Para analizar y diseñar los sistemas digitales es necesario utilizar herramientas que nos permitan representarlos, reducir sus funciones, optimizarlos y construirlos, entre ellas:

Algebra de Boole. Mapas de Karnaugh Método tabular de Quine McKluskey Máquinas de estados Tablas de verdad y otros

Estas herramientas teóricas nos permiten llevar a la práctica a los sistemas digitales e implementarlos de la forma más adecuada, optimizando los parámetros de costo, potencia, espacio, velocidad, etc. Laboratorio de Sistemas Digitales

II

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Los sistemas digitales se clasifican en dos categorías:

Sistemas digitales combinacionales: Son aquellos en los que la salida del sistema sólo depende de la combinación de entrada actual. Sistemas digitales secuenciales: La salida depende de la entrada actual y de las entradas anteriores. Esta clase de sistemas necesitan elementos de memoria que recojan la información de los estados anteriores del sistema.

Para la implementación de los circuitos digitales, se utilizan compuertas lógicas básicas y combinadas tales como: NOT, AND, OR, NAND, NOR, XOR y XNOR, con las cuales se puede diseñar toda la estructura avanzada de los sistemas digitales complejos. La electrónica digital es posiblemente una de las ramas de la electrónica que se ha desarrollado de forma más acelerada y debido a eso es muy importante conocer los elementos y conceptos que forman la base de conocimiento de esta área. Ventajas de los Circuitos Digitales

Resultados predecibles y repetibles. Facilidad de diseño. Flexibilidad. Funcionalidad. Programabilidad. Velocidad Economía. Avance tecnológico constante. Exactitud. Facilidad de almacenamiento. Facilidad para transmisión datos.

En un mundo totalmente analógico los circuitos digitales han tenido un desarrollo exponencial debido a las facilidades que brindan para realizar el control, el almacenamiento y la transportación de la información binaria, debido a estas características, la mayoría de los procesamientos de señales se realizan en forma digital. En el laboratorio de Sistemas Digitales los alumnos deberán realizar la comprobación de los conceptos básicos teóricos más relevantes utilizados dentro de la electrónica digital, aprendiendo con ello a desarrollar las competencias y habilidades para el análisis, diseño, investigación, consulta de manuales, implementación de circuitos digitales, etc. En estas prácticas se presentan los elementos más importantes y las herramientas que permiten realizar el diseño de sistemas digitales. También se ha incluido la actividad de simulación de los circuitos, pues en la actualidad es muy conveniente tener un análisis previo que permita asegurar con un gran porcentaje de veracidad el comportamiento de los circuitos antes de implementarlos físicamente. Aunque el alumno debe considerar que las simulaciones dependen del grado de precisión que se logre con el software con que se implementan y por lo tanto no son totalmente apegadas a la realidad.

Laboratorio de Sistemas Digitales

III

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Tenga en cuenta que el dispositivo programador de memorias con que se cuenta en el laboratorio puede realizar la prueba funcional de la mayoría de los circuitos integrados que se emplean en las prácticas. Para el dispositivo programador SuperPro 610 P el comando de prueba se encuentra en la esquina superior derecha como se muestra en la figura P.2.

Herramienta para prueba de circuitos integrados Figura P.2 Barra de comandos del programa SuperPro 610P Instrucciones para la elaboración del reporte Para la presentación del reporte se deberá cumplir con los requisitos indicados en el desarrollo de cada una de las prácticas, incluyendo:

Nombre de la práctica. Objetivos. Introducción. Procedimiento experimental (gráficas, tablas, comentarios, etc.). Cuestionario. Conclusiones. Bibliografía.

Los criterios de evaluación para el laboratorio son los siguientes: C1 (Criterio de evaluación 1): Actividades previas C2 (Criterio de evaluación 2): Habilidad en el armado de circuitos C3 (Criterio de evaluación 3): Desarrollo y funcionalidad de la práctica C4 (Criterio de evaluación 4): Reporte entregado con todos los puntos indicados

(30%) (10%) (30%) (30%)

Los reportes deberán incluir una portada obligatoria de formato libre con la siguiente información, sin omitir ninguno de los datos. U. N. A. M. F. E. S. C. Laboratorio de: __________________________________________________________________ Grupo: _____________________________ No. de Práctica: _______________________________ Nombre de Práctica: ______________________________________________________________ Profesor: ________________________________________________________________________ Alumno: _____________________________________________________________________ Fecha de realización: _______________________ Fecha de entrega: _______________________ Semestre: ______________________

Laboratorio de Sistemas Digitales

IV

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Bibliografía 1. 2. 3. 4. 5.

M. Morris Mano, Charles R. Kime, Fundamentos de Diseño Lógico y Computadoras, 3ª Edición, España, Pearson Education de México, 2007. Ronald J. Tocci, Sistemas Digitales, Principios y Aplicaciones, 10ª Edición Prentice Hall Hispanoamericana S.A., México, 2007. John F. Wakerly, Diseño Digital, Principios y Prácticas, 3ª Edición, Pearson Education de México, México, 2007. Floyd Thomas L., Fundamentos de Sistemas Digitales, 9ª Edición, Prentice Hall, Madrid, 2006. Balabanian Norman, Principios de Diseño Lógico Digital, CECSA, 1ª Edición, México, 2002. 6. Garza, Garza Juan Ángel, Sistemas Digitales Y Electrónica Digital, Prácticas De Laboratorio (Incluye CdRom), Pearson Educación de México, 1ª Edición, México, 2006.

Laboratorio de Sistemas Digitales

V

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Reglamento interno de los laboratorios de Comunicaciones, Control, Sistemas Analógicos y Sistemas Digitales 1.

Dentro del laboratorio queda estrictamente prohibido. a. b. c. d. e. f. g. h.

Correr, jugar, gritar o hacer cualquier otra clase de desorden. Dejar basura en las mesas de trabajo y/o pisos. Sentarse sobre las mesas Fumar, consumir alimentos y/o bebidas. Realizar y recibir llamadas telefónicas y/o el envío de cualquier tipo de mensajería. La presencia de personas ajenas en los horarios de laboratorio. Dejar los bancos en desorden. Mover equipos o quitar accesorios de una mesa de trabajo a otra sin el consentimiento previo del profesor de laboratorio en turno. i. Usar o manipular el equipo sin el conocimiento previo del profesor. j. Rayar las mesas del laboratorio. k. Energizar algún circuito sin antes verificar que las conexiones sean las correctas (polaridad de las fuentes de voltaje, multímetros, etc.). l. Hacer cambios en las conexiones o desconectar equipo estando éste energizado. m. Hacer trabajos pesados (taladrar, martillar, etc.) en las mesas de las prácticas. 2.

Se permite el uso de medios electrónicos y equipo de sonido (celulares, tabletas, computadoras, etc.) únicamente para la realización de las prácticas.

3.

El alumno verificará las características de los dispositivos electrónicos con el manual.

4.

Es responsabilidad del profesor y de los alumnos revisar las condiciones del equipo del laboratorio al inicio de cada práctica. El profesor reportará cualquier anomalía que pudiera existir (prendido, dañado, sin funcionar, maltratado, etc.) al encargado de área correspondiente o al jefe de sección.

5.

Es requisito indispensable para la realización de las prácticas, que el alumno cuente con su manual completo y actualizado al semestre en curso, en formato digital o impreso, el cual podrá obtener en: http://olimpia.cuautitlan2.unam.mx/pagina_ingenieria.

6.

El alumno deberá traer su circuito armado para poder realizar la práctica, de no ser así no podrá realizar dicha práctica (donde aplique) y tendrá una evaluación de cero.

7.

Para desarrollar trabajos, o proyectos en las instalaciones de los laboratorios, es requisito indispensable que esté presente el profesor responsable, en caso contrario no podrán hacer uso de las instalaciones.

8.

Correo electrónico del buzón para quejas y sugerencias para cualquier asunto relacionado con los Laboratorios ([email protected])

Laboratorio de Sistemas Digitales

VI

Universidad Nacional Autónoma de México

9.

Facultad de Estudios Superiores Cuautitlán

La evaluación del laboratorio, será en base a lo siguiente: A-

(Aprobado); Cuando el promedio total de todas las prácticas de laboratorio sea mayor o igual a 6 siempre y cuando tengan el 90% de asistencia y el 80% de prácticas acreditadas en base a los criterios de evaluación. NA - (No Aprobado); No se cumplió con los requisitos mínimos establecidos en el punto anterior. NP - (No Presentó); con o sin asistencia pero que no haya entregado reporte alguno. 10. Los casos no previstos en el presente reglamento serán resueltos por el Jefe de Sección. NOTA: En caso de incurrir en faltas a las disposiciones anteriores, el alumno será acreedor a las siguientes sanciones por parte del profesor de laboratorio según sea el caso y la gravedad, baja temporal o baja definitiva del grupo de laboratorio al que está inscrito.

Laboratorio de Sistemas Digitales

VII

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 1 Herramientas de prueba para sistemas digitales Tema 1.1 Sistemas digitales y analógicos. Objetivos

Comprobar el funcionamiento y condiciones de trabajo de los circuitos implementados con diodos luminosos (leds). Implementar un circuito con switch de 1 polo 1 tiro (1P1T) que permita insertar valores digitales a los circuitos de las prácticas.

Introducción Para realizar pruebas de una forma más eficiente, en los sistemas digitales es recomendable utilizar elementos de apoyo que permiten visualizar o insertar las señales requeridas por los circuitos digitales. En los sistemas digitales es necesario verificar el estado de varias señales de forma simultánea y debido a que los osciloscopios solo tienen 2 canales es preferible utilizar puntas de prueba con LED´s. También en esta práctica se implementará un circuito que permite insertar señales digitales ( 0 o 1 lógicos) a los circuitos de las prácticas y para hacerlo de una forma más rápida se usará un circuito con switch que permite insertar “0” lógicos o “0 V” y “1” lógicos o “5 V”. En esta práctica el alumno probará ambos circuitos de leds y switch en la tableta de conexiones para comprender su funcionamiento y realizar las observaciones y mediciones necesarias. Las observaciones realizadas sobre el funcionamiento de estos circuitos es muy importante para comprender los diseños posteriores. Actividades Previas a la Práctica 1. 2.

EI alumno deberá realizar la lectura de la práctica de laboratorio. Traer armados los circuitos de las figuras 1.1 y 1.2 en la tableta de conexiones.

Material para la práctica de laboratorio Hoja técnica (Datasheet) del diodo LED XLUG50C impresa o en formato electrónico. 4 Resistencias de 0.47 kΩ a ½ W. 5 Resistencias de 1kΩ a ½ W. 4 Diodos LED del color preferido. 1 DIP switch de 5 posiciones. Equipo 1 Multímetro 1 Fuente de voltaje de CD 1 Tableta de conexiones Laboratorio de Sistemas Digitales

1

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Procedimiento Experimental 1.

Compruebe el comportamiento correcto del circuito de la figura 1.1, observando el encendido y apagado de cada uno de los leds, conectando las terminales de entrada al nivel de 5 V o 0 V respectivamente.

Figura 1.1 2. 3. 4.

Mida y anote la caída de voltaje en la resistencia y la caída de voltaje en el diodo cuando esté encendido. Mida y anote la corriente del diodo cuando esté encendido. Compruebe el funcionamiento del circuito de la figura 1.2 tomando en consideración que las terminales de salida producen 0V o 5V dependiendo de la posición del switch correspondiente y por lo tanto se debe tener cuidado de que las terminales de salida no se toquen entre sí ya que producirían un corto circuito.

Figura 1.2 Cuestionario 1.

De la hoja técnica del diodo LED XLUG50C, localice los valores de los parámetros siguientes y anótelos en la siguiente tabla Corriente en directa Corriente en inversa Corriente pico Potencia Voltaje en directa Longitud de onda pico Ancho espectral Material empleado para la emisión de la luz Tabla 1.1

Laboratorio de Sistemas Digitales

2

Universidad Nacional Autónoma de México

2. 3. 4. 5. 6. 7.

Facultad de Estudios Superiores Cuautitlán

Explique el significado de cada uno de los parámetros mencionados en la pregunta 1 del cuestionario. Explique porque el circuito de la figura 1.1 debe de tener una resistencia en serie con el diodo. Explique porque los diodos LED no deben conectarse de forma directa, sin resistencia, a la salida de un circuito digital. Determine el valor mínimo de resistencia que podría emplearse para no exceder los parámetros del diodo definidos por la hoja de datos. Dibuje el diagrama de los switch: 1 polo 1 tiro (1P1T), 2 polos 1 tiro (2P1T) y 2 polos 2 tiros (2P2T) y explique a que se refiere el concepto polo y tiro. Compruebe matemáticamente los valores de corriente y voltaje analizando la malla del circuito y tomando en cuenta la hoja técnica del diodo LED XLUG50C.

Laboratorio de Sistemas Digitales

3

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 2 Compuertas lógicas integradas Tema 2.2. Compuertas lógicas básicas, sus tablas de verdad y sus expresiones de Boole. Objetivos

El alumno comprobará el funcionamiento los circuitos integrados de las familias lógicas digitales TTL y CMOS El alumno comprobará las tablas de verdad de las compuertas básicas integradas. El alumno comparará los valores de voltaje de las compuertas TTL y las compuertas CMOS.

Introducción En la actualidad existe una gama amplia de familias lógicas digitales, las cuales se implementan en forma de circuitos integrados. De las cuales las familias TTL y CMOS son las más ampliamente comercializadas. Los circuitos integrados de las diferentes familias lógicas se emplean de acuerdo a la aplicación sobre la que serán empleados ya que tienen características muy diversas entre sí, como pueden ser: la potencia consumida, la velocidad de respuesta, su inmunidad al ruido, los voltajes de alimentación, grados de integración, costo, tamaño, encapsulamiento, temperatura de trabajo, etc. La familia TTL es una familia empleada con mucha regularidad en el diseño de sistemas digitales debido a su versatilidad y facilidad de manejo.

Figura 2.1 Los circuitos integrados que contienen compuertas son considerados como circuitos de baja escala de integración (Small Scale Integrated o SSI) puesto que solo contienen de 4 a 10 compuertas y por eso son los elementos básicos de la electrónica digital, pero fundamentales para la construcción de grandes bloques funcionales empleados para la construcción de microprocesadores, memorias y todos los sistemas digitales conocidos. En comparación con las familias lógicas bipolares entre las que se encuentran las TTL, las familias lógicas de tecnología Metal Oxido Semiconductor o familias MOS, tienen tiempos de respuesta mayores, el consumo de potencia es menor debido a que son dispositivos que trabajan en base a voltajes y no en base a corrientes como lo hacen los transistores BJT, el margen de ruido que soportan es mayor debido a que trabajan en estado de encendido o apagado con altas impedancias de dispositivo, poseen un mayor intervalo de suministro de voltaje, un factor de carga más elevado puesto que consumen corrientes muy reducidas y es por eso que una sola salida puede alimentar a muchas entradas. Una de sus características más importantes es que ocupan un área mucho menor dentro de un circuito integrado que sus contrapartes TTL y es por ello que son las compuertas más ampliamente empleadas en la construcción de circuitos integrados de escala de integración muy alta (VLSI), tales como memorias, microprocesadores, microcontroladores, dispositivos lógicos programables y otros. Laboratorio de Sistemas Digitales

4

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Existen diferentes series de la familia CMOS de CI digitales. Donde cada una de ellas cubre una condición de diseño para diferentes dispositivos digitales, entre ellas, compatibilidad con TTL, rango de voltaje, potencia disipada, etc. La serie 4000, que fue introducida por RCA fue la primera familia CMOS. La serie original es la serie 4000A; la 4000B representa una mejora con respecto a la primera y con una mayor capacidad de corriente.

Figura 2.2 En esta práctica el alumno obtendrá las tablas de verdad lógicas y de voltajes de cada una de las compuertas básicas; AND, OR, NAND, NOR, NOT y XOR en ambas familias lógicas TTL y CMOS. Actividades Previas a la Práctica 1. 2. 3.

EI alumno deberá realizar la lectura de la práctica de laboratorio. Realizar la simulación de los circuitos de las figuras 2.5, 2.6, 2.7, 2.8, 2.10 y 2.11. Entregar al profesor los resultados de las simulaciones en forma impresa o digital. Traer los circuitos armados.

Material 1 C.I. 74LS04 1 C.I. 74LS08 1 C.I. 74LS32 1 C.I. 4069 1 C.I. 4071 1 C.I. 4081 2 Resistencias de 0.47KΩ a ½ W. 2 Diodos LED Equipo 1 Fuente de Voltaje de C.D. 1 Multímetro Digital 1 Tableta de Conexiones Desarrollo 1.

Implemente el circuito de la figura 2.3 empleando el circuito integrado 74LS04, considerando que dicho circuito contiene 6 compuertas inversoras, de las cuales solo se empleará 1. Todos los circuitos integrados TTL de la familia 74XX que vamos a emplear en esta práctica, requieren una alimentación de 5 V en la terminal 14 y 0 V en la terminal 7 como se muestra en la figura 2.4, los números mostrados en la figura representan el número de terminal del circuito integrado.

Laboratorio de Sistemas Digitales

5

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

14

8

1

7

V1

5V

Figura 2.3 2.

Figura 2.4

Obtenga la tabla de verdad de la compuerta proporcionando a la entrada el nivel de voltaje adecuado, considerando que un 1 lógico es igual a 5 V y un cero lógico es igual a 0 V y midiendo con el multímetro el voltaje correspondiente en la salida. No conecte aún las resistencias ni los leds. A

S

0V 5V Tabla 2.1 3. 4. 5. 6.

Desconecte la entrada A del circuito, dejando dicha terminal al aire (sin conexión) y analice el funcionamiento de la salida del circuito, explique el comportamiento. Implemente el circuito de la figura 2.5. Obtenga la tabla de verdad lógica de la compuerta en función del encendido o apagado de los leds. Mida los voltajes a la salida de la compuerta considerando que ahora tiene la resistencia y el led y compárelos con los valores obtenidos en el punto 2, indique las diferencias o similitudes.

A

S

0 1

Figura 2.5 7. 8.

Tabla 2.2

Obtenga las tablas de verdad para cada uno de los circuitos 2.6 y 2.7 considerando que ahora el circuito tiene 2 entradas. Observe que la configuración de terminales de los siguientes circuitos es idéntica y por lo tanto solo hay que hacer el intercambio de los circuitos integrados.

Figura 2.6

Laboratorio de Sistemas Digitales

A

B

0

0

0

1

1

0

1

1

S

Tabla 2.3

6

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

A

B

0

0

0

1

1

0

1

1

Figura 2.7

S

Tabla 2.4

9.

Los circuitos que se emplearán a continuación pertenecen a la familia MOS y deben manipularse con cuidado ya que son sensibles a descargas estáticas introducidas al manipularlos y por lo tanto deberán tomarse por las orillas sin tocar de forma directa las terminales. 10. Implemente el circuito de la figura 2.8 empleando el circuito integrado CD4069, considerando que dicho circuito contiene 6 compuertas inversoras, de las cuales solo se empleará 1. Todos los circuitos integrados CMOS de la familia 40XX permiten una alimentación en un rango de 3V a 15 V en la terminal 14 (VDD) y 0 V en la terminal 7 (VSS). 11. Fije el valor de la fuente a 10 V. como se muestra en la figura 2.9. 14

8

1

7

V1

10 V

Figura 2.8

Figura 2.9

12. Obtenga la tabla de verdad de la compuerta proporcionando a la entrada el nivel de voltaje adecuado, considerando que un 1 lógico es igual a 10 V y un cero lógico es igual a 0 V y midiendo con el multímetro el voltaje correspondiente en la salida. No conecte aún las resistencias ni los leds. A

S

0V 10 V Tabla 2.5 13. Desconecte la entrada A del circuito, dejando dicha terminal al aire (sin conexión) y analice el funcionamiento de la salida del circuito, explique el comportamiento. 14. Para los siguientes circuitos no emplee los leds debido a que la relación de resistencias producirá que las mediciones se alteren y por lo tanto deberán hacerse las mediciones solo con el multímetro. 15. Obtenga las tablas para cada uno de los circuitos 2.10, 2.13, 2.14 y 2.16, considerando que ahora se tienen 2 entradas. 16. Observe que la configuración de terminales no cambia y solo es necesario intercambiar el circuito integrado.

Laboratorio de Sistemas Digitales

7

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

A

B

0

0

0

1

1

0

1

1

Figura 2.10

Figura 2.11

S

Tabla 2.6 A

B

0

0

0

1

1

0

1

1

S

Figura 2.7

Cuestionario 1.

2.

3. 4.

5. 6.

Investigue el significado de las siglas correspondientes a cada una de las familias lógicas: RTL, DTL, TTL, IIL, ECL, NMOS, CMOS y dibuje el circuito discreto básico (resistencias, transistores, etc.) para cada una de ellas. Obtenga la hoja de datos (datasheet) del circuito 74LS08 en el sitio www.alldatasheet.com del fabricante On Semiconductor y haga una tabla con los valores típicos de la fuente de alimentación VCC y de los parámetros: VIH, VIL, VOH, VOL, IIH, IIL, IOH e IOL explicando el significado de cada uno de ellos. De las hojas técnicas anteriores investigue los valores de los parámetros tPLH y tPHL denominados tiempos de propagación, comente que significado de cada término Obtenga la hoja de datos (datasheet) del circuito CD4081 en el sitio www.alldatasheet.com del fabricante FAIRCHILD y haga una tabla con los valores típicos de la fuente de alimentación V DD y de los parámetros: VIH, VIL, VOH, VOL, IIH, IIL, IOH e IOL . De las hojas técnicas anteriores investigue los valores de los parámetros tPLH y tPHL . Compare los valores obtenidos en los incisos 2 y 3 con los obtenidos en los incisos 4 y 5 para los circuitos 74LS08 y CD4081 y comente acerca de las semejanzas o diferencias.

Laboratorio de Sistemas Digitales

8

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 3 Compuertas lógicas derivadas Tema 2.2. Compuertas lógicas básicas, sus tablas de verdad y sus expresiones de Boole. Objetivos

El alumno comprobará el funcionamiento las compuertas derivadas. El alumno comprobará las tablas de verdad de las compuertas derivadas. El alumno implementará circuitos digitales combinacionales, definidos a partir de expresiones de Boole y empleando cualquier tipo de compuerta.

Introducción A partir de las compuertas básicas NOT, AND y OR, se pueden obtener otras compuertas derivadas uniéndolas en diferentes configuraciones como las mostradas en la figura 3.1. Entre estas nuevas configuraciones tenemos el BUFFER, la compuerta NAND y la compuerta NOR.

Buffer

NAND

NOR Figura 3.1 Compuertas derivadas En los sistemas digitales, a las compuertas NAND (7400) y NOR (7402) se les denomina compuertas universales debido a que con ambas es posible construir cualquier sistema digital pues debido a sus tablas de verdad pueden implementarse como cualquiera de las compuertas básicas. Por ejemplo, empleando compuertas NAND se puede implementar las compuertas NOT y AND realizando las conexiones indicadas en la figura 3.2.

NOT

AND Figura 3.2

Laboratorio de Sistemas Digitales

9

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Otra compuerta que se puede diseñar es la compuerta OR como se muestra en la figura 3.3.

OR

Figura 3.3. Utilizando las compuertas básicas se desarrollaron otras 2 compuertas muy importantes en el establecimiento de las operaciones aritméticas con sistemas digitales, ya que estas representan las operaciones de suma de bits, estas son las compuertas XOR y XNOR de las cuales se presentan sus expresiones de Boole en forma de suma de productos o minitérminos y sus circuitos en la figura 3.4.

XOR 𝑆 = 𝐴̅𝐵 + 𝐴𝐵̅

XNOR 𝑆 = 𝐴̅𝐵̅ + 𝐴𝐵

Figura 3.4. Debido a que las compuertas XOR y XNOR se emplean en muchas aplicaciones aritméticas y de comunicaciones, los circuitos de la figura 3.4 se han construido en forma de circuito integrado y corresponden a los circuitos 7486 para la XOR en tecnología TTL y 4077 para la XNOR en tecnología CMOS. Una aplicación común de las compuertas XOR es la de inversor controlado, que a través de una señal de control de 1 bit puede seleccionarse que la salida funcione como buffer o como un inversor según lo muestra la figura 3.5. Inversor Controlado

Figura 3.5 Actividades Previas a la Práctica 1. 2. 3. 4. 5.

EI alumno deberá realizar la lectura de la práctica de laboratorio. El alumno hará las simulaciones de los circuitos de BUFFER, NAND y NOR implementados con los inversores de la figura 3.1. El alumno hará las simulaciones de los circuitos de NOT, AND y OR de las figuras 3.2 y 3.3. El alumno hará las simulaciones de los circuitos de XOR y XNOR de la figura 3.4. El alumno hará las simulaciones del circuito Inversor controlado de la figura 3.5.

Laboratorio de Sistemas Digitales

10

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Material 1 C.I. 74LS00 1 C.I. 74LS04 1 C.I. 74LS08 1 C.I. 74LS32 1 C.I. 74LS86 3 Resistencias de 0.47KΩ a ½ W. 3 Diodos LED Equipo 1 Fuente de Voltaje de C.D. 1 Generador de Funciones 1 Multímetro Digital 1 Osciloscopio 1 Tableta de Conexiones. Desarrollo 1. 2. 3. 4. 5.

Implemente los circuitos BUFFER, NAND y NOR de la figura 3.1 conectando los leds y resistencias a las entradas y salidas de cada circuito y obtenga las tablas de verdad para cada uno de ellos. Implemente los circuitos NOT, AND y OR de las figuras 3.2 y 3.3 conectando los leds y resistencias a las entradas y salidas de cada circuito y obtenga las tablas de verdad para cada uno de ellos. Implemente los circuitos XOR y XNOR de la figura 3.4 conectando los leds y resistencias a las entradas y salidas de cada circuito y obtenga las tablas de verdad para cada uno de ellos. Implemente el circuito Inversor controlado de la figura 3.5 conectando los leds y resistencias a las entradas y salidas del circuito y obtenga la tabla de verdad. Inserte en el circuito de la figura 3.5 una señal cuadrada de 1KHz con niveles TTL en la terminal de señal de entrada y observe en el osciloscopio la señal de entrada y la de salida, cambiando de nivel la señal de control

Cuestionario 1. 2.

Convierta el circuito de la figura 3.6 a lógica NAND y dibuje la solución. Compruebe la veracidad de los 2 teoremas de DeMorgan simulando ambos lados de las ecuaciones y comparando las tablas de verdad de cada uno. ̅̅̅̅̅̅̅̅ 𝐴 + 𝐵 = 𝐴̅ ̅ 𝐵 ̅̅̅̅̅ 𝐴 𝐵 = 𝐴̅ + 𝐵̅

Laboratorio de Sistemas Digitales

11

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Figura 3.6.

Laboratorio de Sistemas Digitales

12

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 4 Circuitos combinacionales por álgebra de Boole Tema 2.4. Descripción algebraica de circuitos lógicos. Objetivos

El alumno diseñará un circuito digital para detectar los 6 códigos no válidos del código Exceso 3 (XS3). El alumno implementará el circuito lógico combinacional diseñado empleando compuertas lógicas integradas. El alumno comprobará la validez de la solución obtenida a través de algebra de Boole. El alumno comprobará la tabla de verdad del circuito.

Introducción Los circuitos digitales combinacionales son aquellos en los cuales el nivel lógico de la salida depende solo de la combinación de los niveles lógicos de las entradas presentes en ese instante. Un circuito combinacional no tiene las características de memoria o realimentación que poseen los circuitos secuenciales. Los circuitos combinacionales tienen “n” entradas lógicas con las cuales se puede obtener un conjunto de 2 n combinaciones posibles las cuales pueden ser expresadas en una tabla de verdad como lo muestra la figura 4.1. 2 entradas (A y B)

A

B

1 salida (S)

0 0 1 1

0 1 0 1

22 = 4 combinaciones

S Tabla de verdad

Figura 4.1 Un circuito combinacional puede tener “m” salidas que dependen de un solo conjunto de entradas pero cada una de las salidas es totalmente independiente de las otras y pueden tratarse de forma separada.

Entradas

Circuito Combinacional

A B C D

S1 S2 S3 S4

Salidas

Figura 4.2 Cada una de las salidas S1, S2, S3, etc…, de un circuito combinacional se debe definir a través de su tabla de verdad, de ecuaciones en algebra de Boole o través de afirmaciones y negaciones que definan el comportamiento del circuito para cada una de las posibles combinaciones de entrada. También es posible que para algunas de las combinaciones de entrada no estén definidas las salidas correspondientes y es por ello que se pueden establecer las salidas correspondientes con un valor especial denominado “no importa” (D’ont Care).

Laboratorio de Sistemas Digitales

13

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Estos valores pueden ser considerados para el análisis del circuito de acuerdo a la conveniencia del diseñador, como “1” o “0” lógico ya que al no ser importante su valor para la definición de la salida, este comportamiento no afecta a los términos que son primordiales. En la presente práctica se diseñará un circuito que detectará los 6 códigos no válidos del código Exceso 3. Si el código binario de entrada en 4 bits es un número no válido entonces la salida encenderá un LED indicando la condición de error. El circuito debe contar con 4 entradas (A, B, C y D), donde A es el bit más significativo y una sola salida (detección de código no válido) como se muestra en la figura 4.4. A B C D

Detector de Código no válido

S

Figura 4.4 En esta práctica se debe realizar el desarrollo empleando únicamente álgebra de Boole y no se deben emplear otro tipo de herramientas gráficas o computarizadas. Actividades previas 1. 2. 3. 4. 5. 6. 7.

El alumno deberá realizar la lectura de la práctica. Escriba la tabla de verdad del sistema. Escriba la función de Boole de la tabla de verdad empleando el método de minitérminos. Reduzca la función empleando únicamente álgebra de Boole e incluya todo el desarrollo realizado para obtener la función final. Dibuje el circuito resultante empleando solamente compuertas básicas de 2 entradas. Realice la simulación del circuito e imprima el diagrama correspondiente indicando sobre de él la numeración de las terminales para cada compuerta. Arme el circuito en la tableta de conexiones.

Material Circuitos integrados necesarios para la implementación del diseño 5 resistencias de 0.47kΩ a ½ W. 5 leds. Equipo 1 Fuente de Voltaje de C.D. 1 Multímetro Digital Desarrollo 1. 2. 3. 4.

Arme el circuito diseñado en las actividades previas, adicionando las conexiones necesarias para proporcionar las 4 entradas. Conecte en cada entrada 1 led y una resistencia para visualizar los valores. Conecte 1 led y una resistencia en la salida para comprobar los valores de la tabla de verdad. Compruebe la tabla de verdad considerando que el led de salida debe encenderse cuando el código de entrada es un número no válido.

Laboratorio de Sistemas Digitales

14

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Cuestionario 1.

Diseñe un circuito que compare dos números de 2 bits cada uno y genere dos salidas que indiquen si el número 1 es mayor que el número 2 y otra salida que indique si el número 1 es menor que el número 2.

2. 3.

El número 1 está formado por los bits denominados A y B. El número 2 está formado por los bits denominados C y D. La salida X se enciende si #1 > #2. La salida Y se enciende si #1 < #2.

Empleando únicamente algebra de Boole, realice todos los pasos del diseño e inclúyalos en su reporte. Simule el circuito diseñado y entregue la simulación en su reporte, ya sea impreso o en formato digital.

Laboratorio de Sistemas Digitales

15

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 5 Circuitos combinacionales con mapas de Karnaugh Tema 3.6. Método de simplificación a través del mapa de Karnaugh. Objetivo

El alumno diseñará un circuito lógico combinacional a partir de un problema específico. El alumno empleará el método clásico de diseño (tabla de verdad y minimización por el método del mapa de Karnaugh para obtener las funciones lógicas. El alumno elaborará el diagrama lógico) y realizará la implementación con circuitos lógicos de la familia TTL y/o CMOS.

Introducción El método del mapa de Karnaugh reduce la necesidad de cálculos excesivos realizados con el álgebra de Boole. Este método toma en consideración la capacidad que tenemos los humanos para el reconocimiento de patrones. Los resultados de la tabla de verdad son trasladados a una tabla bidimensional (mapa de Karnaugh), donde las celdas están ordenadas de acuerdo al código GRAY y cada posición representa una combinación de las entradas, mientras que el valor de cada celda representa el valor de salida. Se forman los grupos óptimos de 0’s o 1’s, que representan los términos de la forma canónica de la lógica en la tabla de verdad. D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

C 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

f(D,C,B.A) 0 0 0 1 0 0 1 1 0 1 0 1 0 0 1 1

̅𝑨 𝒇(𝑫, 𝑪, 𝑩, 𝑨) = 𝑩𝑨 + 𝑪𝑩 + 𝑫𝑪

Figura 5.1 Método del mapa de Karnaugh

Laboratorio de Sistemas Digitales

16

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Planteamiento del problema En una línea de producción, unas barras de longitud variable viajan en una banda transportadora. Un brazo mecánico empuja las barras, que están dentro de la especificación (+/-10%), hacia un lado de la banda. Un segundo brazo mecánico empuja las barras, que están muy largas, hacia otro lado de la banda y un tercer brazo empuja las barras cortas.

Figura 5.2 Diagrama para el problema de selección de barras Las barras detectadas como correctas (ver la figura 5.2), están dentro de la especificación (+/-5%) y se mantienen en la banda. La banda transportadora cuenta con cuatro sensores para detectar la longitud de las barras. La figura ilustra la posición de los sensores y la banda transportadora dentro de la línea de producción. Es muy importante que el sensor 1 siempre detecte la barra, porque es una indicación de que dicha barra está alineada para una medición correcta. Tomando en cuenta el planteamiento del problema, diseñar un circuito combinacional para detectar el tamaño de la barra que, a su vez, enviará una señal al brazo mecánico correspondiente. Considerar que los sensores envían un “1” lógico cuando detectan la barra. Actividades previas 1. 2. 3. 4. 5. 6.

Elabore la tabla de verdad del sistema. Obtenga las funciones lógicas del sistema empleando el método del mapa de Karnaugh. Dibuje el diagrama lógico a partir de las funciones lógicas obtenidas. Realice la simulación del sistema y entréguela a su profesor en forma impresa o en formato digital.. Elabore un reporte con los resultados y su discusión de los puntos 1 al 4. Arme el circuito en la tableta de conexiones.

Material El requerido para implementar su diseño. 4 LED´s. 4 Resistencias de 470 Ω. 4 Resistencias de 1 KΩ. 1 DIP Switch de 4 posiciones. Laboratorio de Sistemas Digitales

17

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Equipo 1 Fuente de Voltaje de C.D. 1 Multímetro Digital. Desarrollo 1. 2.

Conectar al sistema diseñado, las resistencias de entrada y salida, así como el DIP Swich y los LEDs; como se muestra en la figura 5.3. Comprobar que el sistema funciona de acuerdo con la tabla de verdad, verificando todas las combinaciones de las entradas y las correspondientes salidas.

+5v

470 ON

1 2 3 4

OFF

8 7 6 5

470

470

470 Salidas Entradas

Sistema diseñado

1K

1K

1K

1K

Figura 5.3 Conexiones de prueba para el sistema diseñado.

Cuestionario 1. 2.

Obtenga las funciones lógicas del problema planteado en la práctica, usando el método tabular de Quine McCluskey. Realizar la simulación del sistema, mostrar el diagrama obtenido y escribir la discusión de los resultados.

Laboratorio de Sistemas Digitales

18

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 6 Características de las familias lógicas Tema 4.2. La familia Lógica Transistor – Transistor (TTL). 4.4. La familia Lógica Metal – Oxido – Semiconductor (MOS). Objetivos

Obtener los valores de los parámetros característicos, de las familias lógicas TTL y CMOS. Diferenciar entre las configuraciones de salida del tipo tótem, colector abierto y tercer estado. Comprobar los valores prácticos de los parámetros de un circuito integrado.

Introducción Los circuitos integrados (CI) digitales, también llamados chip o microchip, se componen internamente de muchos transistores para formar compuertas lógicas que, a su vez, realizarán una función. La escala de integración, es decir, la cantidad de transistores de la cual se compone el CI, determina la complejidad de dicho componente.

Figura 6.1 Compuerta NAND 74LS00.

Existen escalas de integración que van desde cientos (pequeña escala de integración SSI, por sus siglas en inglés), miles (LSI) hasta millones (VLSI) o billones de transistores (VVLSI). Están fabricados de obleas compuestas por un material semiconductor que conduce electricidad bajo ciertas condiciones y no lo hace en otras.

Figura 6.2 Laboratorio de Sistemas Digitales

19

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Las familias lógicas tuvieron su origen en el año de 1970 y continuaron su desarrollo y mejoramiento durante los siguientes años. Las familias lógicas más comunes son TTL (Lógica de Transistor y Transistor) y CMOS (Metal Óxido Semiconductor Complementario). Las compuertas pertenecientes a TTL están construidas con transistores bipolares de una sola juntura (BJT), varios transistores forman una compuerta básica (NAND, NOR, NOT) y varias compuertas están integradas en un sólo circuito, ya sea para formar una función o para usarlas de manera independiente. Por otro lado, las compuertas pertenecientes a la familia CMOS, están construidas con transistores de efecto de campo (FET) hechos de una placa metálica con otro material óxido y semiconductor. Los MOS pueden ser de canal N (N-MOS), en dónde el canal de conducción de la corriente eléctrica está formado por electrones, o de canal P (P-MOS) en los cuáles el canal está formado por los protones. Dentro de las mismas familias lógicas existe otra diferencia en cuanto a la configuración de salida de las compuertas de que se compone. De acuerdo con esta configuración de salida, las compuertas pueden ser de tipo tótem, de colector abierto o de tercer estado.

Figura 6.3 Compuerta NAND con salida Totem Pole.

Figura 6.4 Compuerta NAND con salida de Colector Abierto.

Figura 6.5 Compuerta NAND con salida de tercer estado. Además, si la salida posee amplificadores de corriente, se dice que su salida es del tipo “buffer”. Otra característica que puede poseer la compuerta es que cuente con un circuito comparador con histéresis para acondicionamiento de la señal. Aunque estas familias lógicas tienen muchos años de haberse inventado, la justificación principal para seguirlas usando es que resultan provechosas desde un punto de vista didáctico para reforzar los conocimientos teóricos con la práctica. Laboratorio de Sistemas Digitales

20

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Por lo tanto, en ésta práctica abordaremos el uso de las familias lógicas TTL y CMOS, para conocer sus características principales en cuanto a corrientes, voltajes, factor de carga, tiempo de respuesta y consumo de corriente, implementaremos circuitos combinando ambas familias lógicas. Usaremos circuitos integrados con compuertas de diferente configuración, de los transistores en su salida (tótem pole, colector abierto, tercer estado y salida con “buffer”). Finalmente resaltaremos la importancia del uso de las hojas técnicas para nuestros cálculos durante la etapa del diseño. Actividades previas a la práctica 1. 2. 3. 4.

El alumno realizará la lectura de la práctica y traerá los circuitos armados en la tableta de conexiones. Realizar la simulación de los circuitos de las figuras 6.6, 6.7 y 6.8 y entregar los resultados a su profesor en forma impresa o formato electrónico Para el circuito de la figura 6.6, calcular el valor de voltaje en el punto marcado como “A” y el valor de corriente en el punto marcado como “Salida”, tomando los datos de la hoja técnica del CI 4011. Para el circuito de la figura 6.7, obtener el valor de voltaje de conducción (V df) del LED1 a utilizar, tomar los datos necesarios de la hoja técnica del CI 74LS05 y calcular el valor de R1.

Equipo 1 Fuente de voltaje de CD. 1 Multímetro. Material 1 CI 4011 1 CI 74LS125 1 CI 74LS05 1 Resistencia (R1) del valor calculado. 1 Diodo emisor de luz (LED1). Hojas técnicas de los circuitos empleados, impresas o en formato electrónico. Procedimiento experimental 1.

Arme el circuito mostrado en la figura 6.6.

Figura 6.6 Compuerta CMOS.

2.

Cambie la posición de los conmutadores y llene la tabla 6.1, midiendo el voltaje en las entradas A y B, y el valor de corriente en el punto marcado como “Salida”.

Laboratorio de Sistemas Digitales

21

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Conmutadores SW1 SW2 Cerrado Cerrado Cerrado Abierto Abierto Cerrado Abierto Abierto

Voltaje A B

Corriente Salida

Tabla 6.1 Valores de corriente y voltaje.

3.

Arme el circuito mostrado en la figura 6.7, haciendo uso (en la entrada) de la herramienta de prueba de la práctica 1, colocar la resistencia (R1) del valor calculado y el LED1 seleccionado.

Figura 6.7 Compuerta TTL de colector abierto.

4.

Cambie la posición del conmutador y llene la tabla 6.2 con los valores de voltaje y corriente medidos en el punto marcado como “Salida”. Entrada SW1 Abierto Cerrado

Salida Voltaje Corriente

Tabla 6.2 Valores de corriente y voltaje.

5.

Arme el circuito mostrado en la figura 6.8, haciendo uso de la herramienta de prueba de la práctica 1.

Figura 6.8 Compuerta TTL de tercer estado.

Laboratorio de Sistemas Digitales

22

Universidad Nacional Autónoma de México

6.

Facultad de Estudios Superiores Cuautitlán

Cambie la posición de los conmutadores y llene la tabla 6.3, midiendo el voltaje y la corriente en la entrada C, y en el punto marcado como "Salida". Entradas SW1 SW2 Cerrado Cerrado Cerrado Abierto Abierto Cerrado Abierto Abierto

Entrada C Voltaje Corriente

Salida Voltaje Corriente

Tabla 6.3 Valores de corriente y voltaje.

Cuestionario 1. 2. 3. 4.

5. 6. 7. 8. 9.

Para el circuito de la figura 6.6, comparar los datos obtenidos teóricamente con los resultados de la tabla 6.1 y anote sus observaciones. Calcular la potencia máxima disipada por los circuitos mostrados en las figuras 6.6 y 6.8 Con los datos de la hoja técnica, calcular el margen de ruido de una compuerta NAND del CI 4011, primero al alimentarlo con una fuente de +5v y luego con una fuente de +15v. Con los datos de la hoja técnica, calcular el margen de ruido de una compuerta de tercer estado del CI 74LS125, compare sus resultados con los obtenidos en la respuesta a la pregunta 2 y anote sus observaciones. Con base en los datos de la hoja técnica, determine el tiempo de retardo máximo de una compuerta del CI 4011 y de una compuerta del CI 74LS05, compare los tiempos obtenidos y anote sus observaciones. De acuerdo con los resultados obtenidos en la tabla 6.3, explique el funcionamiento y mencione una aplicación de las compuertas de tercer estado. Con base en los resultados obtenidos en la tabla 6.2, explique el funcionamiento y mencione una aplicación de las compuertas de colector abierto. Tomando en cuenta los datos de la hoja técnica del CI 4011 y del CI 74LS125, determine cuántas compuertas del 74LS05 se pueden conectar a la salida de una compuerta del 4011. Comente su resultado. Conecte la salida de una compuerta del CI 4011 a la entrada de una compuerta del CI 74LS125 y, a su vez, la salida de éste a la entrada de una compuerta del CI 74LS05. Determine cuántas compuertas del CI 74LS05 se pueden conectar a la salida de una compuerta del CI 74LS125. Elabore el diagrama y comente sus resultados.

Laboratorio de Sistemas Digitales

23

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 7 Multiplexores y demultiplexores Tema 5.3. Multiplexores y Demultiplexores. Objetivos

Comprobar el funcionamiento de los circuitos integrados multiplexores y de los circuitos demultiplexores. Implementar una tabla de verdad combinacional empleando un multiplexor. Realizar un sistema de transmisión empleando un multiplexor y un demultiplexor.

Introducción Los multiplexores (MUX) son circuitos de mediana escala de integración (MSI) debido a que en su construcción se emplean algunas decenas de componentes básicos que realizan en conjunto una función específica. Los multiplexores son empleados como selectores de señal que trasladan la información de uno de los múltiples canales de entrada, sobre un canal único de salida y así reducen la necesidad de canales múltiples de transmisión, para realizar esta función requieren señales de control que les permitan seleccionar cuál de los canales de entrada será trasladado a la salida Son muy empleados en los sistemas de comunicación de datos para multiplexar en tiempo (Time Divison Multiplexing o TDM) a varias fuentes de información sobre un canal único de transmisión, en la figura 7.1 se muestra un multiplexor de 4 canales a 1 y 2 señales de control. A este multiplexor se le denomina MUX 4 a 1.

Figura 7.1 Dentro de sus aplicaciones en la electrónica digital se encuentra la implementación de tablas de verdad sin el empleo de compuertas lógicas adicionales o con un mínimo de ellas. Los dispositivos demultiplexores (DEMUX) realizan la función inversa puesto que tienen una sola entrada y múltiples canales de salida. Al igual que los MUX, los DEMUX requieren señales de control a través de las cuales se selecciona en cuál de los canales de salida aparecerá la información del canal de entrada. En la figura 7.2 se muestra un demultiplexor con 1 canal de entrada, 4 canales de salida y sus 2 señales de selección. A este demultiplexor se le denomina DEMUX 1 a 4.

Laboratorio de Sistemas Digitales

24

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Figura 7.2 Como se mencionó anteriormente, para seleccionar el canal de entrada en los multiplexores y el canal de salida en los demultiplexores, se requieren señales de control adicionales que permitan indicarle a los circuitos el número de canal a emplear, la selección es aleatoria y no se requiere entrar y salir por el mismo número de canal. En un multiplexor con 2n entradas, n indicaría el número de líneas de control. En conjunto ambos dispositivos se emplean en los sistemas de comunicaciones para transmitir múltiples canales de información a través de un solo medio físico.

Figura 7.3 Sistema de comunicaciones multiplexado en tiempo Debido a las características tanto de los multiplexores como de los demultiplexores, estos dispositivos son empleados para la implementación de tablas de verdad de sistemas combinacionales, logrando con ello la reducción del número de compuertas lógicas necesarias para realizar un diseño. Actividades Previas 1.

Obtenga la tabla de verdad de la función booleana siguiente. (𝐴, 𝐵, 𝐶, 𝐷) = ∑(0,2,4,5,8,9,11,12,13,15)

2.

Diseñe el circuito que resuelve la tabla de verdad anterior empleando solo un multiplexor de 8 a 1 de tecnología CMOS CD4051E y las compuertas necesarias para su implementación. Diseñe el circuito que resuelve la tabla de verdad anterior empleando solo un multiplexor de 4 a 1 de tecnología CMOS CD74HC153E y las compuertas necesarias para su implementación. Realice la simulación de ambos circuitos y entregue a su profesor los resultados en forma impresa o en formato electrónico. Imprima los diagramas de ambos circuitos diseñados. Arme los circuitos de la actividad previa y del desarrollo en la tableta de conexiones.

3. 4. 5. 6.

Laboratorio de Sistemas Digitales

25

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Material 1 Circuito integrado CD74HC153E 2 Circuitos integrados CD4051BE no comprar equivalentes. Circuitos integrados necesarios para la implementación de los circuitos. 5 Resistencias de 470 Ω a ½ W. 5 Diodos luminosos LED Equipo 1 Fuente de CD 1 Generador de Funciones 1 Multímetro 1 Osciloscopio Desarrollo 1.

2. 3.

4. 5.

Pruebe el circuito diseñado en el punto 2 de las actividades previas considerando que los circuitos integrados son CMOS y por lo tanto deberán alimentarse con una fuente de VDD=10V, además deberán tomarse las precauciones adecuadas para evitar descargas electrostáticas que dañen a los circuitos. Compruebe la tabla de verdad utilizando los leds y resistencias tanto en las entradas como en las salidas. Pruebe el circuito diseñado en el punto 3 de las actividades previas considerando que los circuitos integrados son CMOS y por lo tanto deberán alimentarse con una fuente de VDD=10V, además deberán tomarse las precauciones adecuadas para evitar descargas electrostáticas que dañen a los circuitos. Compruebe la tabla de verdad utilizando los leds y resistencias tanto en las entradas como en las salidas. Implemente el sistema mostrado en la figura 7.4

I0 I1 I2 I3 I4 I5 I6 I7

Figura 7.4 6.

7.

Introduzca una señal cuadrada de 1 kHz y 5 V pico a pico con un offset de 2.5 V, para tener niveles TTL de 0 a 5V, en alguno de los canales de entrada del circuito U1, indicando dicho canal a través de las señales selectoras (A1, B1 y C1) adecuadas, escoja uno de los canales de salida a través de las señales selectoras (A2, B2 y C2) del circuito U2 y verifique con el osciloscopio que la señal de entrada se transfiere a la salida deseada. Repita el proceso para otra entrada y otra salida indicándolas a través de sus entradas selectoras y compruebe como la información es transferida por un único medio físico compartido en tiempo (multiplexación en tiempo).

Laboratorio de Sistemas Digitales

26

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Cuestionario 1. 2. 3. 4.

Consulte el manual de circuitos de la familia CMOS e indique la función que realizan cada una de las terminales del circuito integrado CD4051BE. Indicar la función que realiza la terminal de voltaje VEE en el circuito integrado. Diseñe un sumador de 2 números de 2 bits cada uno (AB)+(CD) empleando multiplexores de 8x1. Modifique el circuito del inciso 5 para que de forma sincrónica la información insertada por el canal 1 salga por el canal 1, la del canal 2 por el canal 2, etc. Haga un diagrama de su diseño.

Laboratorio de Sistemas Digitales

27

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 8 Unidad aritmético lógica (ALU) Tema 5.4. Circuitos digitales para operaciones aritméticas binarias. 5.7. Unidades Aritmético Lógicas (ALU’s). Objetivos

El alumno simulará el funcionamiento de un sumador de 4 bits empleando sumadores completos de 1 bit en cascada. El alumno comprenderá el funcionamiento de una unidad aritmético lógica (ALU) de mediana escala de integración. El alumno comprobará las diferentes operaciones que puede realizar la ALU, tanto aritméticas como lógicas.

Introducción En el desarrollo de la electrónica digital los circuitos de compuertas básicas establecieron la estructura para todos los sistemas digitales subsecuentes. A partir de estas bases se comenzaron a crear circuitos de diferentes características, entre los más importantes fueron los circuitos aritméticos que resolvían operaciones matemáticas básicas tales como los medio sumadores (half sum) y los sumadores completos (full sum). Organizando estos elementos en paralelo o en serie se pueden realizar circuitos aritméticos de un mayor número de bits o con diferentes capacidades. El desarrollo de estos circuitos ha llevado a la creación de unidades aritmético lógicas integradas (ALU´s) y al posterior desarrollo de los sistemas de microprocesadores. La Unidad Aritmético Lógica (ALU 74LS181) es un circuito integrado de mediana escala de integración que contiene un aproximado de 75 compuertas básicas. Este circuito realiza un total de 16 operaciones aritméticas con y sin acarreo y 16 operaciones lógicas sobre dos datos de 4 bits denominados dato A (A3, A2, A1 y A0) y dato B (B3, B2, B1 y B0). Para definir si la operación va a ser aritmética o lógica, se emplea la señal de Modo (M), la cual decide cual conjunto de operaciones se va a realizar. La elección de la operación específica dentro de uno de los conjuntos, aritmético o lógico, se realiza a través de las 4 señales de selección (S3, S2, S1 y S0) e incluye la suma (Plus), la resta (Minus), el decremento, la transferencia directa y las operaciones de AND, OR, XOR, NAND, XNOR, etc. La ALU también cuenta con una señal de acarreo del 4º al 5º bit que puede ser empleada para alimentar el acarreo de entrada de la siguiente ALU. En la figura 8.1 se muestran los canales de entrada del dato A, del dato B, de las entradas de selección, el acarreo de entrada, el modo, el dato de salida, el acarreo de salida y otras señales de control. La ALU puede realizar operaciones en cascada en conjunto con otras ALU’s para poder incrementar el largo de palabra.

Laboratorio de Sistemas Digitales

28

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

En esta práctica se realizará la simulación de un circuito sumador completo de 4 bits y además se comprobarán algunas de las operaciones aritméticas y lógicas con la ALU 74LS181 y se comprobarán los resultados teóricos de dichas operaciones.

Figura 8.1 Una consideración adicional para la implementación de este circuito es que en el manual se proporcionan dos tablas de funcionamiento:

La primera considera que los datos A y B deberán ser insertados en forma invertida a su valor ya que son activos en bajo. La segunda tabla considera que los datos A y B serán insertados en la forma normal puesto que son activos en alto.

En esta práctica consideraremos que los datos se insertaran activos en alto y por lo tanto se utilizará la segunda tabla del manual, mostrada en la tabla 8.1.

Tabla 8.1

Laboratorio de Sistemas Digitales

29

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Actividades previas 1. 2. 3.

Realice la simulación del circuito de la figura 8.2 siguiendo las indicaciones dadas en el desarrollo. Implemente el circuito de la Unidad Aritmético Lógica 74LS181 en la tableta de conexiones. Imprima o descargue la hoja técnica en formato electrónico de la hoja técnica de la ALU 74LS181.

Material 1 Circuito 74LS181 1 Circuito 74LS04 5 Resistencias de 0.47K a ½ W. 5 Diodos luminosos LED Equipo 1 Fuente de CD 1 Multímetro Desarrollo 1. 2. 3. 4.

Implemente el circuito mostrado en la figura 8.2. Elabore una tabla con 4 pares de valores de 4 bits cada uno, para los datos "A" y "B" que serán empleados para las operaciones lógicas y anótelos en la tabla 8.3, los datos deben ser diferentes de cero. Elabore otra tabla con 4 pares de valores de 4 bits cada uno, para los datos "A" y "B" que serán empleados para las operaciones aritméticas y anótelos en la tabla 8.4, los datos deben ser diferentes de cero. Opere sus datos con las operaciones aritméticas y lógicas mostradas en la tabla 8.2. Operaciones Lógicas

Operaciones Aritméticas

AꚚB

A PLUS AB

A+B

A PLUS B

A+B

A PLUS B PLUS 1

AB

A MINUS B Tabla 8.2

5. 6. 7.

8.

Obtenga el código binario de cada operación de la tabla 8.2 empleando la tabla 8.1 y complete las tablas 8.3 y 8.4. Considere que en la tabla de la ALU, el signo (+) indica la operación lógica OR y la palabra (PLUS) indica la operación aritmética de suma así como la palabra (MINUS) indica la resta. Aplique los valores a las líneas de datos "A" y "B" de forma tal que realice las operaciones indicadas, checar en el manual los niveles lógicos que deben aplicarse a las terminales M y C n para las operaciones seleccionadas, anótelos en las tablas 8.3 y 8.4. Anote los resultados de las operaciones en las tablas 8.3 y 8.4 considerando que la salida contiene 5 bits y representa el acarreo de salida y la función realizada (Cn+4, F3, F2, F1 y F0), compruebe los resultados realizando las operaciones en papel e integrándolos al reporte.

Laboratorio de Sistemas Digitales

30

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Figura 8.2 Dato A (4 bits)

Dato B (4 bits)

Selección (4 bits)

Cn (1 bit)

M (1 bit)

Operación

Resultado (5 bits)

Lógicas

Tabla 8.3 Dato A (4 bits)

Dato B (4 bits)

Selección (4 bits)

CN (1 bit)

M (1 bit)

Operación

Resultado (5 bits)

Aritméticas

Tabla 8.4 Cuestionario 1. 2. 3. 4.

Diseñe un circuito sumador completo de 4 bits empleando circuitos sumadores completos de 1 bit en cascada y realice la simulación. Empleando circuitos 74LS181, diseñe una Unidad Aritmética Lógica capaz de operar 16 bits en paralelo y simule su comportamiento. Explique el concepto de acarreo anticipado (Carry Look Ahead) empleado en las ALU´s. Investigar en los manuales de TTL. Explique la función que tienen las terminales de los pines 14, 15, 16 y 17 del circuito 74181.

Laboratorio de Sistemas Digitales

31

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 9 Contador síncrono para control de motor de pasos Tema 6.7. Aplicaciones de circuitos secuenciales. Objetivos

Implementar un circuito secuencial que genere las señales de activación de las bobinas de un motor de pasos. Implementar el circuito secuencial, empleando Flip-Flops JK. Comprobar el funcionamiento del circuito en interacción con un motor de pasos de 3 terminales.

Introducción El motor de pasos es un dispositivo eléctrico que requiere un conjunto de señales secuenciales aplicadas en sus bobinas para producir un movimiento rotacional discreto de su eje, su rotor gira un determinado ángulo por cada pulso de entrada, existen motores con 15º por pulso y 24 pulsos para una vuelta y también de 0.9º por pulso y 400 pulsos por vuelta, aunque cada día se va reduciendo el tamaño del paso así como aumentando la potencia del motor. Un motor de pasos puede ser comparado con una serie de electro magnetos o solenoides dispuestos en círculo como se muestra en la figura 9.1.

Bobinas

Bobinas

Figura 9.1 El resultado de este movimiento es un posicionamiento preciso y confiable que puede controlarse de forma directa por un sistema que genere los pulsos digitales con la secuencia, la velocidad y el número suficiente para poder realizar controles de posición, velocidad o sentido de giro. La secuencia de señales necesarias para mover a un motor de pasos de 4 hilos y 3 fases, se muestra en la figura 9.2 en la cual se puede indicar que el sentido de giro depende del orden en que se apliquen las señales, de izquierda a derecha o de derecha a izquierda, en función de la gráfica.

Laboratorio de Sistemas Digitales

32

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Los niveles de voltaje son TTL. V C B A

t Figura 9.2

La velocidad depende de la frecuencia de aplicación de las señales, más frecuencia más velocidad y la posición depende del número de pulsos insertados. En la actualidad podemos encontrar estos motores en, unidades de disco duro, impresoras, robots, máquinas herramientas, juguetes, cámaras, autos y cualquier otra aplicación que requiera una precisión muy alta para el control de velocidad o posición. En la presente práctica se implementará un circuito que genera las señales necesarias para mover al motor de acuerdo al diagrama de estados mostrado en la figura 9.3, considerando que el estado inicial es cero. El motor empleado es un motor de 3 bobinas que serán alimentadas por cada uno de los 3 transistores y un alambre común que será alimentado con 12 VCD.

ABC = 000 Señales del motor de pasos

Figura 9.3 Actividades Previas 1.

2. 3.

4.

Realice el análisis del diagrama de estados a través de la tabla de estados empleando cualquier tipo de Flip Flops (tipo D o tipo JK), determine los estados siguientes de acuerdo al diagrama e inserte un “no importa” para todos los estados no considerados, obtenga las ecuaciones de excitación y reduzca para obtener el circuito correspondiente. Implemente el circuito correspondiente. Realice la simulación del circuito secuencial diseñado sin considerar al motor de pasos ya que no se cuenta con un motor de pasos de 3 terminales en las librerías del simulador, por lo tanto solo compruebe el funcionamiento con los leds en las salidas. Arme el circuito diseñado en la tableta de conexiones y adicione la etapa de potencia a cada una de las salidas de su circuito como se muestra en la figura 9.4.

Laboratorio de Sistemas Digitales

33

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Material Material necesario para implementar el diseño secuencial 4 Resistencias de 0.47KΩ a ½ W. 3 Resistencias de 56 Ω a ½ W. 3 Transistores TIP31 4 Diodos luminosos LED Equipo 1 Fuente de CD 1 Generador de Funciones 1 Multímetro 1 Motor de Pasos proporcionado por el laboratorio Desarrollo 1.

Arme el circuito diseñado y las etapas de potencia mostradas en la figura 9.4.

Salida A

Reloj

Circuito Secuencial Diseñado

Salida B

Salida C

Figura 9.4 2. 3. 4. 5. 6. 7. 8. 9.

La señal de reloj del circuito secuencial es una señal de cuadrada de 1 Hz. y niveles de voltaje TTL. El motor de pasos tiene 3 terminales de color (naranja, rojo y café) que van conectadas a los 3 colectores de cada uno de los transistores en el orden indicado. El alambre negro del motor se conecta a VCC = 12V. Coloque los leds en cada una de las salidas del circuito secuencial diseñado y en el reloj del circuito. Compruebe que la secuencia generada a las salidas del circuito secuencial es la correcta. Compruebe que el motor gira de forma continua en la secuencia adecuada. Incremente paulatinamente la frecuencia de la señal de reloj, observe y anote el comportamiento del motor y su velocidad. Identifique y anote el valor de la frecuencia máxima del reloj para la cual el motor de pasos aún tiene un funcionamiento adecuado.

Laboratorio de Sistemas Digitales

34

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Cuestionario 1.

2.

Diseñe un circuito de control para el mismo motor de pasos, que contenga una señal de entrada adicional que sirva para invertir la secuencia de conteo de (1 – 2 – 4) a (4 – 2 – 1) con lo cual el motor invertirá el sentido de giro. Realice la simulación de su diseño con solo los leds de salida y entregue en forma impresa o en formato electrónico los resultados.

Laboratorio de Sistemas Digitales

35

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 10 Autómatas finitos con máquinas de Moore y Mealy Tema 6.8. Autómatas finitos. 6.8.1. Máquina de Mealy. 6.8.2. Máquina de Moore. Objetivos

Diseñar un sumador completo de 1 bit en serie. Comprobar el funcionamiento del circuito sumador serie de 1 bit a través de una máquina de Mealy y una máquina de Moore. Analizar las semejanzas y diferencias que presentan ambos diseños.

Introducción En esta práctica se diseñarán 2 autómatas finitos para solucionar el mismo problema del sumador serie de 1 bit pero desde 2 puntos de vista diferentes, el primer diseño se realizará empleando una máquina de Mealy y el segundo diseño empleando una máquina de Moore. La máquina de Mealy es una máquina de estados finita o autómata finito, donde las salidas del sistema están determinadas por el estado actual y las entradas y donde estas señales de salida se obtienen a través de un circuito combinacional. Esto significa que en el diagrama de estados se debe indicar el estado que tendría la señal de salida para cada elemento de transición. Por ejemplo, en la trayectoria de un estado 001 a un estado 101, si la entrada X es cero y la salida S es uno, se debe poner sobre la transición la etiqueta “0/1” que corresponde a la nomenclatura “X/S” como se muestra en la figura 10.1. 0/1

001

101 Figura 10.1

Por otro lado una máquina de Moore es una máquina de estados finita o autómata finito, donde la salida actual depende solo del estado actual y no depende de la entrada actual. Por lo tanto, los estados de una máquina de Moore producen la definición total del sistema. La entrada actual es utilizada para realizar el cambio de estado, pero las salidas están autocontenidas en el código del estado siguiente de la máquina de estados. Por ejemplo, en la trayectoria del estado 000 al estado 101 para una entrada X = 1, la salida S es 0 para el estado 000 y la salida S es 1 para el estado 101, considerando que la entrada X = 1 solo se emplea para cambiar de estado y esta acción se indica poniendo el valor de la entrada sobre la transición, figura 10.2. El bit de salida está integrado en el estado y se marca en rojo con el bit menos significativo. Laboratorio de Sistemas Digitales

36

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

X=1

000

101 Figura 10.2

Diseño con máquina de Moore En esta práctica se diseñará el sistema secuencial de encendido de las luces de un auto. Para ello utilizaremos una máquina de Moore. Cada uno de los 4 diferentes estados de las 2 luces se representan de acuerdo a la tabla 10.1, considere que los valores de los 2 bits del estado representan al mismo tiempo las dos salidas del sistema, el bit más significativo es la luz izquierda y el bit menos significativo es la luz derecha. Estado I D 00 01 10 11

Definición de Estados Ambas apagadas Derecha encendida Izquierda encendida Emergencia Tabla 10.1

Las señales de entrada I, A, D y E son independientes y solo una de ellas está activa a la vez. Para reducir el número de señales de entrada y observando que solo hay 4 posibilidades, entonces con solo 2 bits de codificación se pueden representar los 4 tipos de entrada, para este proceso se tiene un circuito codificador de 4 entradas a 2 que asumimos como verdadero y no está presente en la práctica. Las transiciones entre estados deben cumplir las siguientes condiciones en función de las entradas codificadas a 2 bits como las mostradas en la tabla 10.2. Entradas IADE 0001 0010 0100 1000

Entradas codificadas a 2 bits 00 01 10 11

Definición Emergencia Derecha encendida Ambas apagadas Izquierda encendida

Tabla 10.2.

Cuando la palanca de las direccionales se coloque en la posición DERECHA, se deberá encender y apagar de forma intermitente la luz identificada como D, de forma síncrona con un reloj de 1 Hz. Cuando la palanca de las direccionales se coloque en la posición IZQUIERDA, se deberá encender y apagar de forma intermitente la luz identificada como I, de forma síncrona con un reloj de 1 Hz. Cuando la palanca se coloque en la posición central (APAGADO) no se encenderá ninguna luz.

Laboratorio de Sistemas Digitales

37

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Cuando se active el interruptor de EMERGENCIA, se activarán ambas luces simultáneamente, y se desactivarán ambas de forma síncrona con el reloj, independientemente de la posición de la palanca, es decir, la entrada de emergencia tiene prioridad absoluta.

De las definiciones y asignaciones de las tablas 10.1 y 10.2 y utilizando el método de máquina de Moore, se obtuvo el diagrama de la figura 10.3. En el cuál se plantearon todas las posibilidades del sistema exceptuando condiciones no permitidas como cuando 2 señales de entrada se activan simultáneamente ya que esos casos no están contemplados.

Figura 10.3. Actividades Previas 1. 2. 3. 4. 5.

El alumno deberá realizar la lectura de la práctica. El alumno deberá generar la tabla de estados definida por el diagrama de estados de la figura 10.3. El alumno deberá diseñar el circuito que soluciona el problema empleando Flip Flops de cualquier tipo y la lógica combinacional necesaria para su establecimiento. El alumno realizará la simulación del circuito diseñado y entregará a su profesor en forma impresa o en formato electrónico los resultados. Traer armado en la tableta de conexiones el circuito diseñado.

Material Circuitos integrados y material para implementar su diseño. Equipo 1 Fuente de CD 1 Generador de Funciones 1 Multímetro Desarrollo 1. 2. 3.

Implemente el circuito diseñado para el sistema de luces. Introduzca una señal de reloj de 1 Hz para poder verificar el cambio del circuito. Compruebe la tabla de estados inicializando el Flip Flop a cero a través del reset de los Flip Flops.

Laboratorio de Sistemas Digitales

38

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Cuestionario 1.

Investigue la definición formal para una máquina de Mealy y para una Máquina de Moore. 2. Diseñar un circuito secuencial que admita como entradas dos líneas A y B, procedentes de dos registros de corrimiento con salida serie, los cuales comparten el reloj en forma síncrona y que insertan 1 bit por cada línea A o B, en cada ciclo de reloj. En la salida del circuito de 2 bits (Z1, Z0) se debe ver codificado en binario, el número de ceros que faltan por introducir al sistema considerando el conteo de ceros de ambas líneas, hasta que éste (el número de ceros introducidos) sea un múltiplo de 4. Suponer que Z1 es la línea más significativa de la salida y que el estado inicial, es decir, cuando todavía no se ha introducido ningún cero, es el mismo que el estado correspondiente a introducir un número de ceros que sea múltiplo de 4. Se debe utilizar la asignación de estados y la definición mostrados en la tabla 10.3. Estado

Codificación Q1 Q0

q0

0 0

q1

0 1

q2

1 0

q3

1 1

Definición Inicial. El número de ceros introducidos es múltiplo de 4 Faltan por introducir tres ceros para que el número de ceros sea múltiplo de 4 Faltan por introducir dos ceros para que el número de ceros sea múltiplo de 4 Falta por introducir un cero para que el número de ceros sea múltiplo de 4 Tabla 10.3

En la figura 10.4 se muestra el diagrama de estados correspondiente.

Figura 10.4 Laboratorio de Sistemas Digitales

39

Universidad Nacional Autónoma de México

3. 4.

Facultad de Estudios Superiores Cuautitlán

Obtener la tabla de estados. Circuito para el autómata finito empleando cualquier tipo de Flip Flops y considerando una máquina de Mealy en donde las salidas se definen de manera independiente del estado. 5. Simulación del sistema

Laboratorio de Sistemas Digitales

40

Universidad Nacional Autónoma de México

Facultad de Estudios Superiores Cuautitlán

Laboratorio de Sistemas Digitales Práctica 11 Memorias ROM Tema 6.7. Aplicaciones de circuitos secuenciales. 7.5. Características de las memorias ROM. Objetivo

Utilizar las memorias de sólo lectura (ROM) como unidades de almacenamiento de información y control.

Introducción Las memorias de solo lectura (ROM) son un tipo de memorias no volátiles que se utilizan en dispositivos electrónicos como unidades para almacenar grandes cantidades de información. Los datos contenidos en la memoria pueden ser modificados, pero con dificultad y de una manera muy lenta. Es por esta razón que se usan principalmente para almacenar firmware (software que está directamente relacionado al hardware) y software de aplicación. En esta práctica utilizaremos la memoria ROM como un dispositivo donde guardaremos los datos necesarios para configurar el controlador de una pantalla de cristal líquido (LCD) para, posteriormente, poder desplegar caracteres.

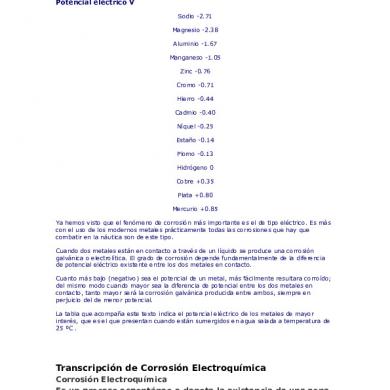

Tabla 11.1 Comandos para el controlador del LCD. Laboratorio de Sistemas Digitales

41